Update:

Tina provides 555 models in both Spice and Spice Macros. I swapped out the pure Spice model with a Spice Macro and Vo now follows that load vs. voltage drop graph closely.

My apologies to Xeno for drifting off of the overshoot issue!

Chris

I am sorry that I missed your point. Sarcasm now noted

vis a vis R vs RC vs no load on the output.

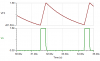

So, in an attempt to simulate the overshoot problem in LTSpice, I joined the LTSpice Yahoo! public forum today and went looking for accurate 555 models. Attached is the first transistor model I found. When run "as is" in LTSpice (as a re-triggered monostable) there are oscillations in the output high state as the timing capacitor approaches a certain level of charge.

I have no idea what the oscillations mean, and have not yet had time to "play" with this particular model. That means I haven't been able to verify the accuracy of this model against "real" circuitry. Also, I am very much a novice in learning to use LTSpice, despite many years of being "exposed" to the technology of Spice simulation. I tend to think along the lines of

Bob Pease with regard to SPICE simulation, but am prepared to change as personal computers and SPICE models continue to improve.

Anyway, this particular transistor model is at least a baby step towards simulating, and perhaps understanding, the cause of the overshoot in

@Xeno Xenox bread-board circuit. I will continue looking for a better model, and perhaps decimate this one to just the output stage for test purposes, but the "proof" is in the reality of a powered-up real component with real oscilloscope measurements, not in how well a SPICE simulation reproduces that behavior.

OTOH, if I can inject some parasitic inductance and/or capacitance into the model and observe the same overshoot that appears in the "real deal," that will lend some credence to the idea that it is an implementation artifact rather than a deficiency of the 555.

@CDRIVE I looked at TINA several years ago but never used it. LTSpice seems to be the

de facto standard for SPICE simulation today, at least in the hobbyist community, and maybe for professional design as well. It may be possible to import TINA SPICE models into LTSpice, so I will look into that too.

Despite some serious misgivings about model accuracy, I like the "look and feel" of LTSpice, so I will probably continue to become more familiar with it... as long as that doesn't cut into the time available for prototyping real circuits.

Hop