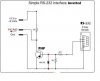

I have tested the max3232 that i have on breadboard with 0.4uf caps and different test with 1uf caps (could not get 0.1 electrolytic) and i got the same 5V cd on the input of the rs232 but 0 volt on the output of ttl.

-

Categories

-

Platforms

-

Content