Hi all!

Currently working my way through a project assigned for class, heres the basics:

1) when switches 1,2,3,4 are thrown in that order, you can throw switch 5 to light the diode.

OR

2) when switches 1,2,3,4,6,7,8 are thrown (in that order), you can then throw switch 5 to light the diode.

OR

3)when switches are thrown in this order 1,6,2,7,3,8,4 then 5, the diode should light.

Any incorrect order of switches and the diode should not light.

-can use any logic gates, inverters and clocked d or j/k flip flops

Basically, its a three step process.

-Design ckt to light when 12345 are thrown

-design ckt to take 1,2,3,4 switches inputted into a ckt that contains logic for switches 6,7,8,

-merge the two ckts together so that when either 1,2,3,4,5 are thrown or 1,2,3,4,6,7,8,5 are thrown, diode lights.

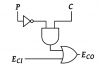

The problem I'm having is taking the 6,7,8 output and combining it with the 1,2,3,4 ckt so that they work together correctly. I guess I just cant figure out which combo of gates to use. Obviously, it cant just be a simple OR gate, because the ckt should not light when switches 6,7,8 are thrown without previously having thrown switches 1,2,3,4. Switch 5 is the "ignition" switch. I have attached my design so far. Any thoughts?

So basically,

1+2+3+4+5=diode on

OR

1+2+3+4+6+7+8+5 = diode on

Any of those out of order or not flipped should and the diode should stay off.

If you could, please take a look at my design and feel free to ask any questions or make suggestions.

Currently working my way through a project assigned for class, heres the basics:

1) when switches 1,2,3,4 are thrown in that order, you can throw switch 5 to light the diode.

OR

2) when switches 1,2,3,4,6,7,8 are thrown (in that order), you can then throw switch 5 to light the diode.

OR

3)when switches are thrown in this order 1,6,2,7,3,8,4 then 5, the diode should light.

Any incorrect order of switches and the diode should not light.

-can use any logic gates, inverters and clocked d or j/k flip flops

Basically, its a three step process.

-Design ckt to light when 12345 are thrown

-design ckt to take 1,2,3,4 switches inputted into a ckt that contains logic for switches 6,7,8,

-merge the two ckts together so that when either 1,2,3,4,5 are thrown or 1,2,3,4,6,7,8,5 are thrown, diode lights.

The problem I'm having is taking the 6,7,8 output and combining it with the 1,2,3,4 ckt so that they work together correctly. I guess I just cant figure out which combo of gates to use. Obviously, it cant just be a simple OR gate, because the ckt should not light when switches 6,7,8 are thrown without previously having thrown switches 1,2,3,4. Switch 5 is the "ignition" switch. I have attached my design so far. Any thoughts?

So basically,

1+2+3+4+5=diode on

OR

1+2+3+4+6+7+8+5 = diode on

Any of those out of order or not flipped should and the diode should stay off.

If you could, please take a look at my design and feel free to ask any questions or make suggestions.