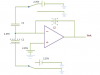

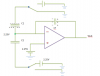

I am going to use the MS3110 to measure capacitance in a MEMS device, below is the function block diagram of this chip.

and the transfer function of this circuit is

I tried to derive the transfer function, but I met a problem which is that I think amplifier here is used as an integrator, the noninverting input and inverting input of the amplifier should have the same potential which is 2.25V, but the inverting input is also determined by the capacitor array on the left side of the diagram, I was stuck here, hope anyone could help me with the derivation of the transfer function. Thanks!

and the transfer function of this circuit is

I tried to derive the transfer function, but I met a problem which is that I think amplifier here is used as an integrator, the noninverting input and inverting input of the amplifier should have the same potential which is 2.25V, but the inverting input is also determined by the capacitor array on the left side of the diagram, I was stuck here, hope anyone could help me with the derivation of the transfer function. Thanks!