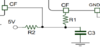

CF is an output (open drain) of the driver IC. R1/C3 form a low pass filter. This filter will suppress any high frequency spikes on the CF output which can arise due to the high power switching operation of the IC.

R2 is required to generate a high signal to the µC when CF is inactive. The ratio of R1/(R1+R2) needs to be such that for a low output at CF of the controller IC (assume 0 V) the voltage at the CF input of the µC is still recognized as low.

Thinking in TTL levels this means that V(CF_µCin) needs to be <= 0.8 V. With R1 = 1 kΩ and R2 = 4 kΩ this voltage will be V(CF_µCin) = 5 V × 1 / (1 + 4) = 1 V which is to much for a reliable TTL level. In this case R2 needs to be higher. I recommend 10 kΩ.

Thinking in CMOS levels this means that V(CF_µCin) needs to be <= 1.5 V (assuming the µC is powered by 5 V), so here 1 k and 4 k would be o.k.

You need to study the datasheet of the µC you are using to find out which situation you have. It is always a good idea to leave some safety margin between the low level input threshold of the µC and the max. low level voltage at C3. Use my above calculations as a starting point for your own.