Hi,

Please allow me to describe my situation first.I recently bought a capacitve readout sensor from a small Japanese company. Although this product is no longer manufactured several years ago, the company still has some inventory, so I could get some chip, but no evaluation board and no technical people answering my question when I try to build my own evaluation board.

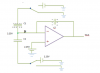

What I have now is the evaluation board circuit diagram and a blurry picture of real object I got from the manual, as shown below.

This readout sensor has three channels X,Y,Z, each channel can measure the difference between two external capacitors,for example Cx1-Cx2. The capacitors share one common electrode which is directly connected to pin SI on the chip.

There is a buffer(see the red arrow) which is used to reduce noise.

From the circuit diagram we can see

1.the non-inverting input is connected to SI;

2. inverting input and output are connected together

3. the connected inverting input and output are separated later.

My question where should I connect the separated inverting input and output to?

I am trying to answer this question by comparing the diagram with the real object. But I found something confusing.

1.The SI pin in the picture of the real object(red arrow)seems isolated from the SI port on the port.

2.I think the two holes on top of and at the bottom of the SI pin should be the inverting input and output in the circuit diagram, but what's the point of making such wiring.

Please allow me to describe my situation first.I recently bought a capacitve readout sensor from a small Japanese company. Although this product is no longer manufactured several years ago, the company still has some inventory, so I could get some chip, but no evaluation board and no technical people answering my question when I try to build my own evaluation board.

What I have now is the evaluation board circuit diagram and a blurry picture of real object I got from the manual, as shown below.

This readout sensor has three channels X,Y,Z, each channel can measure the difference between two external capacitors,for example Cx1-Cx2. The capacitors share one common electrode which is directly connected to pin SI on the chip.

There is a buffer(see the red arrow) which is used to reduce noise.

From the circuit diagram we can see

1.the non-inverting input is connected to SI;

2. inverting input and output are connected together

3. the connected inverting input and output are separated later.

My question where should I connect the separated inverting input and output to?

I am trying to answer this question by comparing the diagram with the real object. But I found something confusing.

1.The SI pin in the picture of the real object(red arrow)seems isolated from the SI port on the port.

2.I think the two holes on top of and at the bottom of the SI pin should be the inverting input and output in the circuit diagram, but what's the point of making such wiring.