Question derived from experiment 11 from Make:Electronics 2nd edition by Charles Platt.

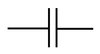

The author explains that when Q1's base is positively biased, Q1 begins sinking current from the left side of C1. Also the right side of C1 goes momentarily below zero volts.

My thought is that current can only sink from the left side of C1 if the right side of C1 has a path back to the left side of C1. Assuming this is true, the right side of C1 must be traveling through Q2; however, since the base of Q2, a NPN transistor, is negatively biased Q2 is "closed" not allowing the path to complete back to the left side of C1.

So how is the capacitor passing current through Q1? What assumption am I making that is incorrect? Any help would be greatly appreciated.

The author explains that when Q1's base is positively biased, Q1 begins sinking current from the left side of C1. Also the right side of C1 goes momentarily below zero volts.

My thought is that current can only sink from the left side of C1 if the right side of C1 has a path back to the left side of C1. Assuming this is true, the right side of C1 must be traveling through Q2; however, since the base of Q2, a NPN transistor, is negatively biased Q2 is "closed" not allowing the path to complete back to the left side of C1.

So how is the capacitor passing current through Q1? What assumption am I making that is incorrect? Any help would be greatly appreciated.