My homework is to design a binary, bi-directional(up/down), preselectable, and self correcting counter from D flip-flop that counts from 0 to10 and from 10 to 0 if we change the direction of counting.

So, there're two schematics i've found and tried to get my counter work well. I am not into in it at all and it seems far too difficult to me. So i need your help.

Schematics "A":

I myself could successfully get my counter to count "up" and go back to zero if the output is "1010". But that's all i could do so far.

https://www.electronicspoint.com/attachment.php?attachmentid=6040&stc=1&d=1351812491

Schematics "B":

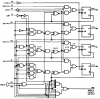

I found a datasheet of a counter IC that contains D flip flops and many gates. Here it is:

https://www.electronicspoint.com/attachment.php?attachmentid=6038&stc=1&d=1351812067

I then tested it with Multisim and it worked pretty well. Although I simplified it and I missed its "ripple carry output"

https://www.electronicspoint.com/attachment.php?attachmentid=6039&stc=1&d=1351812211

It now counts from 0 to15 and 15 to 0

Which of the schematics would it be easier to modify? (I think it'd be schematics "B" but I am not sure how can i do this? What should I do to get it work as it should? Help me if you can. Thanks.

So, there're two schematics i've found and tried to get my counter work well. I am not into in it at all and it seems far too difficult to me. So i need your help.

Schematics "A":

I myself could successfully get my counter to count "up" and go back to zero if the output is "1010". But that's all i could do so far.

https://www.electronicspoint.com/attachment.php?attachmentid=6040&stc=1&d=1351812491

Schematics "B":

I found a datasheet of a counter IC that contains D flip flops and many gates. Here it is:

https://www.electronicspoint.com/attachment.php?attachmentid=6038&stc=1&d=1351812067

I then tested it with Multisim and it worked pretty well. Although I simplified it and I missed its "ripple carry output"

https://www.electronicspoint.com/attachment.php?attachmentid=6039&stc=1&d=1351812211

It now counts from 0 to15 and 15 to 0

Which of the schematics would it be easier to modify? (I think it'd be schematics "B" but I am not sure how can i do this? What should I do to get it work as it should? Help me if you can. Thanks.