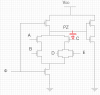

Here is the Logic, I forgot to add Z(output) out of the NOT Gate.

Anyway, I understood that Dynamic Logic is controlled by MOSFET's internal capacitance,

I thought MOSFET A-E's internal capacitance will charged, but I knew that this is not correct

(I didn't know that PZ has parralel capacitor.)

if this right, I thought that when Φ is 1, Capacitor PZ discharges to left N-FET, Z(output) is on, even Φ is 1 cause Z's capacitor(like PZ Cap).

And another question.

if A,B is closed and left P-fet off,N-fet on -> Can PZ cap discharge? Cap will have GND to any side.