The change you need to make is to apply a negative voltage to the gate, not a positive one. This will turn the JFET OFF, i.e. make it STOP conducting. With 0V between its gate and source, a JFET will CONDUCT. This is different from junction transistors and MOSFETs, both of which need a source of bias voltage at their control terminal before they will conduct.

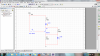

Here's a diagram showing the gate supply battery reversed. The second part is a simple two-LED indicator that shows the voltage on the drain (the "output" of the JFET, in this configuration) on two LEDs.

The top LED, LED1, coloured green, illuminates when the drain voltage is low (close to the 0V rail), which occurs when the JFET is ON (conducting). This will happen when the gate switch is OFF and the gate-source voltage is zero (R

GS pulls the gate to 0V when SW1 is OFF).

The bottom LED, LED2, coloured red, illuminates when the drain voltage is high (close to the VCC rail, which could also be called VDD), which occurs when the JFET is OFF (not conducting). This will happen when the gate switch is ON and the gate-source voltage is negative (from the gate voltage supply battery, BT2).