Hi there medic

Sorry for the slow response. Your circuit looks pretty good. I wouldn't describe you as an electronics newbie!

I have a few comments, most of which are probably just me being paranoid. I'll start with the simple ones.

1. Naming of VIN label

I would call it VBAT or VBATT, since that's what it connects to.

2. Clarify nodes that connect to the PIC

It's obvious from the drawing that the nodes marked CHARGE_STATUS and LATCH_PWR connect to somewhere else on the drawing, but that's not obvious for the SWITCH_STATE node. It's perfectly valid and useful to name a node that's only connected locally. I suggest that you somehow indicate that this node connects elsewhere. Either add an unconnected line, marked with the node name, or perhaps add the text "TO PIC" or give the IC reference and pin number that it connects to.

Now the functional issues.

3. Battery charger IC

I'm not familiar with the MCP73831 battery charge controller that you're using as U2 but I don't see any problems.

4. CHARGE_STATUS signal source resistance

You're feeding the STAT output of the MCP73831 through a voltage divider of two 100k resistors, and into the ADC in the PIC. I understand why you're doing this, but I'm a bit worried that the source resistance of this signal (i.e. the output resistance of the voltage divider) may be too high to get reliable conversions.

In the past, I have had problems getting clean conversions with successive approximation ADCs because of the current pulses they fire back from their input pins. I have had to add smoothing capacitors from the pin to 0V (or AGND) to provide a stable voltage to the pin. Values around 10 nF worked well. Avoid cheap multi-layer ceramics though; they can become leaky. With the capacitor, the actual driving impedance can be quite high. Of course, adding capacitance also slows down the response to changes on that output from the battery charger.

You could also reduce R6 and R7, but you don't want to waste power.

I'm not sure if this will be an issue with your PIC but you might want to test for it by connecting a scope on the analogue input pin while conversions are being performed, or writing test code to see how stable the converted value is.

5. Turn-off circuit: R4 not needed

R4 in the pushbutton circuit shouldn't be needed. The voltage on C11 will never be more than about 0.6V because it's limited by the base-emitter voltage of Q2, so R8 will pull D2 pin 1 to that voltage, and D2 has a forward voltage to overcome.

6. Turn-off circuit: U3 part type and CE pin pulldown

You haven't specified the full part number for U3, the XC6219 LDO regulator. You MUST specify the full part number - some of the characters in the suffix specify parameters that are critical to the circuit's operation.

Characters 2, 3 and 4 obviously depend on your output voltage requirements, and characters 5, 6 and 7 obviously depend on the package you want.

Character 1 selects between the 150 mA version and the 300 mA version (the choice obviously depends on how much current you need to draw from it) and between four options for the CE (chip enable) pin.

You have already chosen devices with an active high CE input, which means letters A, B, E and F. Only the B and F devices are described as "standard"; the others are described as "semi-custom" so it may be wise to avoid those.

If you use a "standard" device - type B (150 mA) or type F (300 mA) - you'll need an external pulldown resistor on the CE, since those types don't have built-in pulldown resistors. You could move R4 over to the CE pin.

Your full part number for U3 would be:

- XC6219B33txy-G (150 mA)

- XC6219F33txy-G (300 mA)

where t is "1" for 1% output voltage tolerance or "2" for 2% output voltage tolerance, and xy are the package designation letters.

7. Turn-off circuit: CE voltage threshold and saturation of Q2

To guarantee that the XC6219 will turn OFF, you have to take the CE pin below the maximum V

CEL voltage. This voltage is 0.25V as shown on the data sheet:

(That table applies to types A and B, but that parameter is the same for all types.)

My concern is whether there will be enough base current to saturate Q2 to the point where it will reliably pull the CE pin below the 0.25V threshold.

I'm going to look at the collector current assuming VBAT is 4.0V because that gives the highest current through R3, which is the worst case. Then I'm going to look at the base current assuming VBAT is 3.0V because that is the worst case. This is not really fair because both worst cases can't exist at the same time, but engineering is one place where it's good to be conservative.

I've used LTSpice to test a simulated transistor. You haven't specified the component type for Q2 so I used a BC847B. Here is the test schematic.

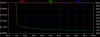

The simulation applies a base current that ramps steadily from 0 µA to 10 µA. I graphed the base current I

B in blue, the base voltage V

B in red (just for interest), and the collector-emitter voltage V

C in green. This is the result.

This screen shot shows only the bottom part of the graph. The green trace starts at the supply voltage, 3.4V, at the left side of the graph, but we're only interested in the section where V

C goes below 0.25V.

You can see the base current rising smoothly to 10 µA over the full 10 ms simulation period. Therefore, the millisecond markers along the X axis correspond directly to microamps of base current. Base voltage is pretty stable at around 0.61V.

The collector voltage doesn't drop below the 0.25V chip enable threshold until the base current has reached slightly over 1 µA, and it doesn't go comfortably below that threshold until the base current is around 2 µA. It seems pretty clear that a BC847B will pull its collector safely below the 0.25V threshold, but this simulation uses a typical BC847B. I don't know how a worst-case BC847B will behave. Or a worst-case of whatever transistor type you decide to use.

Will you get reliable power supply shutdown with 2 µA of base current into Q2? I don't know. At these low currents, leakage currents, that can usually be ignored, can become significant.

It might be better to use an N-channel MOSFET with a low V

GS threshold voltage instead of a transistor for Q2. A MOSFET will pull its drain down closer to 0V than a bipolar junction transistor, and it doesn't draw any significant gate current, which is important, because the currents in the C11 circuit are very low (see later).

The FDV301N is widely used, and looks suitable. Here are the gate threshold limits from the data sheet:

8. Turn-off circuit: leakage in C11.

You need to consider leakage in C11.

When S1 is closed, your R8/R9 circuit is equivalent to a 375k resistor connected to a voltage of half the VIN rail voltage. Let's assume that's at minimum voltage; say 3.0V. So C11 is being charged from a 375k resistor from 1.5V. You need C11 to reach around 0.7~1.1V (assuming you use an FDV301N for Q2) in the power-off button hold time period, currently 15 seconds.

Assuming a worst case V

GS(th) of 1.1V, the voltage drop across the theoretical 375k resistor is (1.5V - 1.1V) = 0.4V. Maximum current through a 375k resistor will be about 1.0 µA. Most electrolytics have maximum specified leakage currents much higher than that!

Reducing the feeding resistance and increasing the capacitance may not help, since the worst case leakage current for most electrolytics is specified in proportion to their capacitance! Reducing the power-off button hold time would be an option.